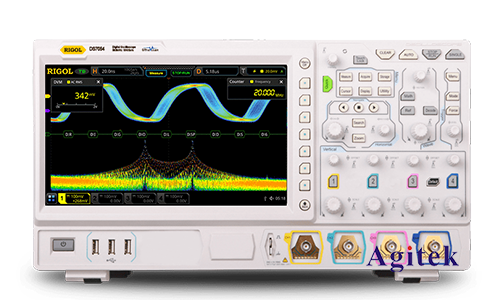

普源示波器逻辑分析仪功能

普源精电作为国内领先的测试测量仪器厂商,其生产的示波器整合逻辑分析仪功能,极大地提升了产品的实用性和性价比。下面将深入探讨普源示波器整合逻辑分析仪的功能特性,涵盖其硬件架构、软件功能以及应用场景。

硬件架构与核心技术

普源示波器整合逻辑分析仪功能的核心在于其混合信号采集架构。不同于传统的分立式示波器和逻辑分析仪,普源的混合信号示波器采用单一硬件平台,通过多通道采集卡,同时实现模拟信号和数字信号的采集与分析。这不仅降低了成本,更重要的是提高了测量效率,避免了不同仪器之间数据同步的难题。

其硬件架构主要包括以下几个关键部分:

高速ADC(模数转换器):负责将模拟信号转换为数字信号,其采样率直接决定了示波器的带宽和精度。普源示波器采用高性能ADC,确保对高速模拟信号的精确捕捉。

逻辑分析仪通道:这是整合逻辑分析仪功能的关键部件,通常采用高速数字输入接口,例如MISO/MOSI、I2C、SPI、UART等,可根据具体型号支持不同数量的通道和协议。这些通道能够采集数字信号的电压电平变化,并将其转换为逻辑状态(高电平或低电平)。

FPGA(现场可编程门阵列):FPGA是整个系统的核心控制单元,负责控制ADC、逻辑分析仪通道、以及数据处理单元。其高速并行处理能力,确保了实时采集和分析的大量数据。

嵌入式处理器:负责运行示波器的操作系统和应用程序,提供用户界面和数据处理功能。强大的嵌入式处理器可以支持更复杂的分析和测量功能。

内存:用于存储采集的波形数据和逻辑分析数据。高速、大容量的内存能够确保对长时间信号的连续采集和存储。

软件功能与应用场景

普源示波器整合的逻辑分析仪功能并非简单的数字信号采集,其软件功能丰富,能够满足多种应用场景的需求。主要功能包括:

多种数字协议解码:支持多种常用的数字通信协议解码,例如I2C、SPI、UART、CAN、LIN等。解码后的数据以用户友好的方式显示,方便用户理解和分析通信过程。这大大简化了调试嵌入式系统的工作量。

逻辑状态分析:能够以逻辑状态图的形式显示数字信号的时序关系,方便用户分析数字信号的时序特性,识别出潜在的逻辑错误。

触发功能:提供多种触发方式,例如边沿触发、脉冲宽度触发、模式触发等,能够精确地捕捉到感兴趣的事件,提高测量效率。复杂的触发条件设置能够满足更细致的调试需求。

搜索和测量功能:允许用户在采集的数据中搜索特定的逻辑状态或事件,并进行相应的测量,例如脉冲宽度、周期、上升沿时间等。

波形和逻辑数据联合显示:这是混合信号示波器的核心优势,能够将模拟信号波形和数字逻辑状态同步显示,方便用户分析模拟信号和数字信号之间的关系,从而更好地理解系统的工作原理。例如,可以同时观察电机控制信号的PWM波形和对应的电机转速。

数据导出与报告生成:支持将采集的数据导出为多种格式,例如CSV、BMP等,方便用户进行进一步的数据处理和分析。部分型号可以生成专业的测量报告,便于存档和分享。

普源示波器整合逻辑分析仪功能的应用场景非常广泛,包括:

嵌入式系统开发与调试:用于分析嵌入式系统的通信协议、时序特性等。

电力电子控制系统调试:用于分析电力电子系统的控制信号、开关波形等。

汽车电子系统测试:用于分析汽车电子系统的CAN总线通信、LIN总线通信等。

工业自动化控制系统调试:用于分析工业自动化控制系统的数字信号、控制逻辑等。

普源示波器整合逻辑分析仪功能,实现了测试测量仪器的功能集成与性能提升,显著提高了测试效率和成本效益。其丰富的软件功能和广泛的应用场景,使其成为众多工程师和科研人员的理想选择,

技术支持

关注官方微信

关注官方微信