什么是抖动?

从本质上讲,抖动是将信号的实际边缘与您希望它所在的位置进行对比。如果信号的边缘太远,它会导致系统出错。“总体抖动”可以分解成多个分量,每个由不同的原因造成,代表设计中的不同问题。在高速系统的设计和调试中,必不可少地要了解不同的抖动分量和关键的分析技巧(解释眼图)。抖动属随机噪声。对于大多数可重复和一致性的测量,要使用有效值,而不是峰峰值的统计测量。用峰峰值和有效值的关系评估抖动分布特性。

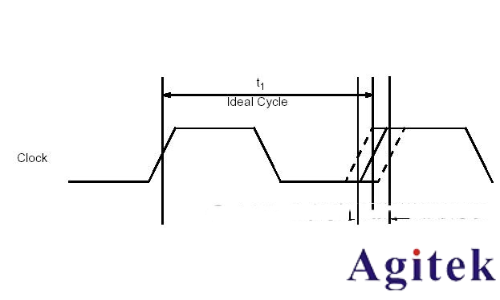

抖动的定义 - 信号的某特定时刻相对于其理想时间位置上的短期偏离为抖动。

简单来说,抖动是指相对于其应当发生跳变的时间,信号实际跳变时有多长时间的提前或延迟。对于数字信号而言,这个有效瞬时就是信号的跳变点(或交叉点)。这取决于时间参考是来自于采样数据,还是由外部提供。如果抖动发生在采样点跳变阈值的“错误位置”,并且导致接收电路“错解”了该比特位发射时的真实情况,那么就会出现传输误差。

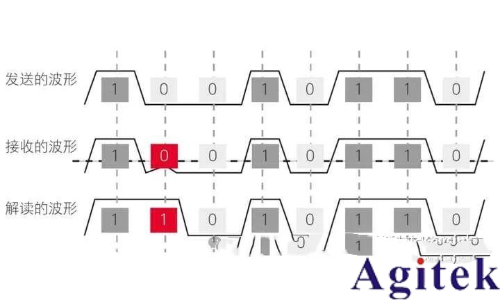

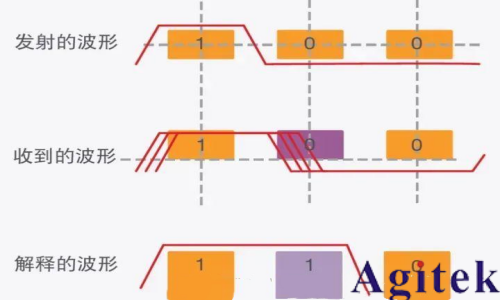

图 1 就是对这种情形的描述。

图 1. 抖动会导致接收机错误地解读被传输的数字数据。

工程师如能了解抖动的类型及成因,熟悉器件特性和各类抖动测试优势,便可轻松地确认抖动的根源,从而有效地消除抖动对电路和产品的影响。

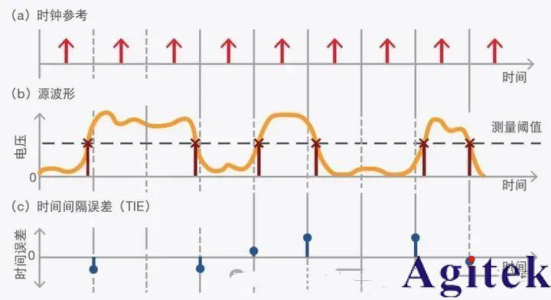

图 2 抖动是在边沿上发生的噪声和相位变化

抖动是在边沿上发生的噪声和相位变化,它们会导致信号时序错误。举个简单的例子,图2中的橙色迹线是一个基本的数据信号。为了分析串行数据应用中使用的嵌入式器件,要从输入的数据流中提取出参考时钟,并与接收机的输入信号结合使用来重建数据。参考时钟在时钟恢复电路中产生,它使接收机可以在本质上“查看”理想间隔的时间点。它可以看到信道在每个点上的电压。根据从这个过程中解释出来的内容,它可以重建数据流,该数据流最终应与发射机发送的数据流完全一致。

但是,如果信号中出现了大量抖动,就会出现问题。如果接收信号中的很多比特位含有大量抖动,那么它们将无法正确地与参考时钟同步。这意味着接收机最终可能在每个时钟周期中收到错误的比特,因此会错误地解码数据。

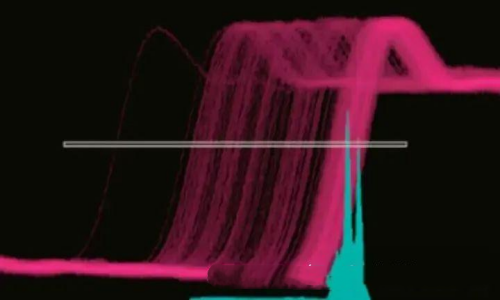

图2中绿色迹线上的红色“x”游标表示信号有抖动时发生的时序误差。请注意,在某些情况下,上升沿或下降边会出现得太快或太晚。这可以在使用余辉显示模式的示波器上看到(见图 3)。如果上升沿出现得太晚,那么接收机会错误解释该比特。边沿交叉点实际发生的时间与理想情况下应发生的时间之差称为时间间隔误差(TIE)。

边沿交叉点实际发生的时间与理想情况下应发生的时间之差称为时间间隔误差(TIE)。

图 3. 使用余辉显示模式显示信号,您会看到时序上出现微小误差(称为 TIE)。

为什么要关注抖动?- 抖动影响了数字系统的性能和可靠性

在同步系统如 SDH, 传输时钟抖动影响子系统的同步, 过大的抖动直接造成误码, 或减低了信号的消光比 ER (等同电信号的信噪比 SNR)。所以 ITU-T, Bellcore, ANSI 都制定模板Mask来检定眼图是否拥有过大的抖动,以及测量传输时钟抖动漂移。

传统的并行式数据通信,即多通道数据与时钟分别传送,往往因为PCB阻抗不匹配,传输路径不一致而产生建立与保持时间违反。当速度增加的时候,准确控制传输时延显得异常的困难,今天新颖的数据通信都已经是串行了, 不单只使用一对差分线来传送数据,以减低信号EMI的干扰,更往往将时钟嵌入在数据中, 而接收端则使用 CDR 从数据中恢复时钟出来。 所以,若数据的抖动过大,频率过高,接收端的 CDR 将无法恢复时钟而导致误码。 所以需要控制系统的时钟与输出的数据抖动。

抖动直接减小了逻辑数字系统的建立保持时间的余量, 严重的影响逻辑运作。

正如我们之前提到的,如果您的信号未与参考时钟同步并且抖动超出了容限值,接收机最终将错误地解释该比特。举一个简单的例子,请参见图4中的情况。发送的数据是二进制的 100。但是,在接收到的波形中存在一些抖动,这导致第二个比特在接收机中显示为 1,而实际上发送的比特为 0。因此,接收机解码得到的结果为 110。

图 4. 接收机错误地解释了含有抖动的发送脉冲

无论您的设计有多好,接收到的信号中总会有一定数量的比特出错。错误比特的数量与发送比特的总数之比称为比特误码率(BER)。显然您希望这个数字尽可能低,而且一定要低于特定标准规定的目标;例如,USB 3.0 规定的比特误码率为 1E-12。要限制 BER,您必须了解导致这些误码的各种抖动。

技术支持

关注官方微信

关注官方微信